## Section 1 – Program Mission and Educational Objectives Oregon Tech Mission:

Oregon Institute of Technology, an Oregon public university, offers innovative and rigorous applied degree programs in the areas of engineering, engineering technologies, health technologies, management, and the arts and sciences. To foster student and graduate success, the university provides an intimate, hands-on learning environment, focusing on application of theory to practice. Oregon Tech offers statewide educational opportunities for the emerging needs of Oregonians and provides information and technical expertise to state, national and international constituents.

### **Core Theme 1: Applied Degree Programs**

Oregon Tech offers innovative and rigorous applied degree programs. The teaching and learning model at Oregon Tech prepares students to apply the knowledge gained in the classroom to the workplace.

### **Core Theme 2: Student and Graduate Success**

Oregon Tech fosters student and graduate success by providing an intimate, hands-on learning environment, which focuses on application of theory to practice. The teaching and support services facilitate students' personal and academic development.

### **Core Theme 3: Statewide Educational Opportunities**

Oregon Tech offers statewide educational opportunities for the emerging needs of Oregon's citizens. To accomplish this, Oregon Tech provides innovative and rigorous applied degree programs to students across the state of Oregon, including high-school programs, online degree programs, and partnership agreements with community colleges and universities.

### **Core Theme 4: Public Service**

Oregon Tech will share information and technical expertise to state, national, and international constituents.

**Program Mission:** The mission of the Embedded Systems Engineering Technology (ESET) bachelor's degree program within the Computer Systems Engineering Technology (CSET) Department at Oregon Institute of Technology is to prepare our students for productive careers in industry and government by providing an excellent education incorporating industry-relevant, applied laboratory-based instruction in both the theory and application of embedded systems engineering. Our focus is educating students to meet the growing workforce demand in Oregon and elsewhere for graduates prepared in both hardware and software aspects of embedded systems. Major components of the ESET program's mission in the CSET Department are:

• To educate a new generation of ESET students to meet current and future industrial challenges and emerging embedded systems engineering trends.

- To promote a sense of scholarship, leadership, and professional service among our graduates.

- To enable our students to create, develop, apply, and disseminate knowledge within the embedded systems development environment.

- To expose our students to cross-disciplinary educational programs.

- To provide industry and government employers with graduates in embedded systems engineering and related professions.

#### **Mission Alignment:**

Our program is very hands-on and thus aligns with Core Theme 1. Our graduates are in high demand by the industries we support. This is evidence that we are aligned with Core Theme 2. The program features two years of project-based learning environment with junior project and senior project.

## Section 2 – Program Description and History

## **Program History**

The Embedded Systems Engineering Technology (ESET) program was proposed to OUS in spring of 2006 and approved in August, 2006. The curriculum for the ESET program is common with the hardware and software programs for the freshman year. The sophomore year of the ESET program has been constructed to mirror the track through both the Computer Engineering Technology (CET) and Software Engineering Technology (SET) programs, called the Concurrent Degree program. The ESET program junior year is when ESET students get instruction specific to topics of embedded systems engineering. These courses were taught for the first time in fall, 2008 on the Klamath Falls campus and soon after at the Wilsonville location. The full program is now offered to students at both locations.

## **Program Enrollment**

Enrollment in the Embedded Systems Engineering Technology program has seen a 115.6% growth. Growth has been faster on the Portland-Metro campus versus the Klamath Falls, campus.

Computer Systems Eng Tech Headcount - Fall 4th Week May 2, 2019

Student location is based on the primary campus assigned to each student; however students may enroll at other/multiple locations. Majors with asterisk (\*) have been phased out.

Dual Majors are reported under each separate major.

| Computer Systems Eng Tech | Fall 2014 | Fall 2015 | Fall 2016 | Fall 2017 | Fall 2018 |

|---------------------------|-----------|-----------|-----------|-----------|-----------|

| Computer Engineering Tech | 81        | 86        | 63        | 62        | 61        |

| Klamath Falls             | 77        | 78        | 57        | 60        | 57        |

| Full-Time                 | 68        | 70        | 51        | 50        | 48        |

| Part-Time                 | 9         | 8         | 6         | 10        | 9         |

| Portland-Metro            | 4         | 8         | 6         | 2         | 4         |

| Full-Time                 | 1         | 8         | 4         |           |           |

| Dort Time                 | 2         |           | 2         | 2         | А         |

| Embedded Systems Eng Tech | 32        | 35        | 57        | 57        | 69        |

| Klamath Falls             | 23        | 24        | 35        | 36        | 42        |

| Full-Time                 | 21        | 24        | 31        | 29        | 36        |

|                           | 2         |           | 4         | 7         | 6         |

| Portland-Metro            | 9         | 11        | 22        | 21        | 27        |

| Full-Time                 | 2         | 4         | 11        | 10        | 14        |

| Part-Time                 | 7         | 7         |           | 11        | 13        |

| Software Engineering Tech | 200       | 205       | 202       | 272       | 270       |

| Klamath Falls             | 173       | 177       | 147       | 157       | 159       |

| Full-Time                 | 145       | 153       | 124       | 126       | 133       |

| Part-Time                 | 28        | 24        | 23        | 31        | 26        |

| Portland-Metro            | 116       | 128       | 136       | 116       | 111       |

| Full-Time                 | 53        | 46        | 62        | 51        | 51        |

| Part-Time                 | 63        | 82        | 74        | 65        | 60        |

| Grand Total               | 402       | 426       | 403       | 392       | 400       |

Figure 1 CSET Headcount

## **Program Graduates**

Program graduates remained flat for both Embedded Systems and Computer Engineering Technology.

Majors with asterisk (\*) have been phased out. Dual Majors are reported under each separate major.

| Computer Systems Eng Tech | 201314 | 201415 | 201516 | 201617 | 201718 |

|---------------------------|--------|--------|--------|--------|--------|

| Assoc of Engineering      | 9      | 15     | 8      | 5      | 2      |

| Klamath Falls             | 8      | 12     | 7      | 4      | 2      |

| Computer Engineering Tech | 7      | 6      | 5      | 3      | 1      |

| Software Engineering Tech | 1      | 6      | 2      | 1      | 1      |

| Portland-Metro            | 1      | 3      | 1      | 1      |        |

| Computer Engineering Tech |        |        | 1      |        |        |

| Software Engineering Tech | 1      | 3      |        | 1      |        |

| Bachelor of Science       | 35     | 43     | 53     | 54     | 50     |

| Klamath Falls             | 22     | 29     | 30     | 26     | 21     |

| Computer Engineering Tech | 3      | 3      | 3      | 6      | 3      |

| Embedded Systems Eng Tech | 1      | 4      | 3      | 5      | 2      |

| Software Engineering Tech | 18     | 22     | 24     | 15     | 16     |

| Portland-Metro            | 13     | 14     | 23     | 28     | 29     |

| Embedded Systems Eng Tech |        | 1      |        | 1      | 2      |

| Software Engineering Tech | 13     | 13     | 23     | 27     | 27     |

| Grand Total               | 44     | 58     | 61     | 59     | 52     |

#### Figure 2 CSET Degrees

### **Employment Rates and Salaries**

Institutional data indicates that graduates of the Embedded Systems Engineering Technology program are successful in finding employment. Some recent employers include Intel, Aristocrat, Mentor Graphics, LO3 Energy, Ravensclaw, Intel, Ravensclaw and Mentor Graphics. Some graduates are also pursuing graduate degrees in a related field.

| Oregon Tech Graduate Outcome D          | ata  |        |         |          |      |       |       |         |        |         |    |        |        |       |

|-----------------------------------------|------|--------|---------|----------|------|-------|-------|---------|--------|---------|----|--------|--------|-------|

| a=2015 / 2016 / 2017 combined           | % Em | ployed | % Conti | nuing Ed | % Se | eking | % Not | Seeking | Succes | ss Rate | [  | Mediar | n Sala | ary   |

|                                         |      |        |         |          |      |       |       |         |        |         |    |        |        |       |

| 0=2016 / 2017 / 2018 combined           | а    | b      | а       | b        | а    | b     | а     | b       | а      | b       |    | а      |        | b     |

| % among those reporting outcomes        | 90.0 | 89.9   | 6.7     | 7.0      | 2.8  | 2.5   | 0.5   | 0.5     | 97.2   | 97.5    | \$ | 58,000 | \$     | 60,00 |

| Computer Engineering Technology         | 100  | 93     | 0       | 7        | 0    | 0     | 0     | 0       | 100    |         | \$ | 64,000 | \$     | 65,50 |

| Embedded Systems Engineering Technology | 88   | 75     | 13      | 13       | 0    | 13    | 0     | 0       | 100    | 87      | \$ | 60,000 | \$     | 60,00 |

| Software Engineering Technology         | 93   | 89     | 0       | 1        | 5    | 8     | 2     | 2       | 95     | 92      | \$ | 65,000 | \$     | 67,00 |

|                                         |      |        |         |          |      |       |       |         |        |         |    |        |        |       |

Figure 3 Employment Data

### Showcase Learning Experiences

- On April 4<sup>th</sup>, 2018 Larry Landis, Senior Manager at Intel PSG came to campus to give a talk on 'Getting hired in tech' as well as run a workshop on 'Timing Analysis'.

- On May 5<sup>th</sup> 2018, Junior project students participated in the campus wide project symposium to showcase their projects. Industry Advisory Board members were also invited to attend.

### **Program Changes**

The program recently acquired the following new equipment towards the end of the 2018-2019 school year totaling \$24,537.00 The equipment acquired will help keep labs up to date.

- 13 Rigol MSO1104 Mixed Signal Oscilloscopes

- 11 Rigol DG1022Z 25 MHz Waveform Generators

- 13 Rigol DP832 Programmable DC Power Supplies

- 2 Pico 2205A Picoscopes

- 20 ICD4 Programmer/Debugger

- 20 Explorer 16/32 Development boards with PIC32MX460 processors

- 2 Chipwhisperer Lites

- 10 UNI-T UT61E Multimeters

- 2 Salae Logic Analyzer

Intel PSG also recently donated 10 DE10-Lites and 2 Stratix 10 development boards. The DE10-Lite boards will be used for CST 162/133 Digital Logic I/II. The Stratix 10 will be used in CST 351.

George Drouant was hired as Instructor on the Klamath Falls campus. He will teach CST 130, CST 131, CST 204, CST 250, CST 315, and other courses to support the Computer Engineering Technology and Embedded Systems Engineering Technology programs. Below is his background.

#### EDUCATION

- M.S. Engineering and Applied Sciences, University of New Orleans

- M.S. Biomedical Engineering, Tulane University

- M. E. Electrical Engineering, Tulane University

- B.S. Engineering Science, University of New Orleans

- Pursuing Ph.D. in Engineering and Applied Sciences, University of New Orleans

- Research Area: Signal processing of Sperm Whale echolocation clicks

#### BACKGROUND

- Over 25 years industry experience at companies which include Lockheed Martin, Jacobs Engineering, LSU Health Science Center, and Tulane Medical School

- Licensed Professional Engineer in Electrical Engineering

## **Program Improvement Discussions**

On September 18, 2019 Enrollment was discussed. ESET enrollment was up 115.6% and CET enrollment was down 24.6%.

CET faculty discussed why enrollment was down. Ideas mentioned were 'Embedded is the hot topic right now'. It was suggested that we investigate what other schools are doing, and further investigate how we can move enrollment in a positive direction. However, the main concern we expressed was that the Technology is the biggest impediment to program success for the Computer Engineering Technology program.

Program faculty discussed CST 136 and EE 321. It was decided that students may end up in different roles and perhaps through advising students could choose to take CST 136 or EE 321. This change is approved pending discussions with EERE.

We discussed offering microcontrollers for EERE but also noted the challenge of our pre-requisite chain.

## **Industry Advisory Board Meeting**

On May 5, 2018 at 9 AM, we held our department IAB meeting to discuss key issues affecting our programs.

Key issues discussed included:

- 1. Management proposed a reduction of CST 337 and CST 331 from 5 credits to 4 credits, eliminating one lab section. IAB strongly voiced their opinion in opposition of this change. They indicated the hands-on time with Doug Lynn was one of the crucial pieces of developing their engineering skills.

- 2. Wire wrapping is not really necessary as modern designs are spun out to PCB.

- 3. We discussed a shift to the Engineering degree which has been awaiting approval. IAB voiced their opinion in support of moving towards Engineering.

- 4. IAB indicated that removal of CST 136 was a bad idea if it was not replaced with something of similar value.

IAB notes were reviewed on September 18, 2019 by program faculty. One proposed item in question was regarding reducing the CST 337 and CST 331 labs from two labs per week to one lab per week. CET and ESET faculty determined that reducing lab time would result in a negative impact to the program learning outcomes and that it should not be implemented. Doug Lynn, the instructor of both classes indicated that the labs would need to be reduced in intensity and would need to become turnkey, resulting in reduced learning.

## **Core Program Faculty**

Douglas Lynn, Professor (KF)

Kevin Pintong, Program Director Computer Engineering Technology, Associate Professor (KF)

Michael Healy, Assistant Professor (KF)

George Drouant, Instructor (KF)

Phong Nguyen, Assistant Professor (PM)

Pramod Govindan, Instructor (PM)

Troy Scevers, Program Director Embedded Systems Engineering Technology, Associate Professor (KF)

## Section 3 – Program Student Learning Outcomes

The mission of the Embedded Systems Engineering Technology (ESET) Degree program within the Computer Systems Engineering Technology (CSET) Department at Oregon Institute of Technology is to prepare our students for productive careers in industry and government by providing an excellent education incorporating industry-relevant, applied laboratory based instruction in both the theory and application of embedded systems engineering. Our focus is educating students to meet the growing workforce demand in Oregon and elsewhere for graduates prepared in both hardware and software aspects of embedded systems. Major components of the ESET program's mission in the CSET Department are:

- 1. To educate a new generation of Embedded Systems Engineering Technology students to meet current and future industrial challenges and emerging embedded systems engineering trends.

- 2. To promote a sense of scholarship, leadership, and professional service among our graduates.

- 3. To enable our students to create, develop, apply, and disseminate knowledge within the embedded systems development environment.

- 4. To expose our students to cross-disciplinary educational programs.

- 5. To provide government and high tech industry employers with graduates in embedded systems engineering and related professions.

### **Program Educational Objectives**

The Program Educational Objectives reflect those attributes a student of the ESET program will practice in professional endeavors.

- Graduates of the ESET program are expected to understand the societal impact of embedded systems and technological solutions.

- Graduates of the ESET program are expected to do hardware/software co-design for embedded systems. Graduates will continue to develop skills in analysis, approach, optimization, and implementation of embedded systems.

- Graduates of the ESET program are expected to obtain the knowledge, skills and capabilities necessary for immediate employment in embedded systems

- Graduates of the ESET program are expected to participate in life-long learning to be able to adapt to a changing environment.

#### **Program Student Learning Outcomes**

(1) an ability to apply knowledge, techniques, skills and modern tools of mathematics, science, engineering, and technology to solve well-defined engineering problems appropriate to the discipline; (ESLO Inquiry and Analysis)

(2) an ability to design solutions for well-defined technical problems and assist with the engineering design of systems, components, or processes appropriate to the discipline;

(3) an ability to apply written, oral, and graphical communication in well-defined technical and non-technical environments; and an ability to identify and use technical literature; (ESLO Communication)

(4) an ability to conduct standard tests, measurements, and experiments and to analyze and interpret the results; (ESLO Quantitative Literacy)

(5) an ability to function effectively as a member of a technical team. (ESLO Teamwork)

### **Program Student Learning Outcomes Update**

On September 18, 2019, the ESET and CET faculty met to review and approve changes to the mission statement, and program student learning outcomes. The ABET ETAC a-k were updated to reflect changes to ABET ETAC 1-5 as of the 2019-2020 cycle. These changes will be discussed in the Fall 2019 Industry Advisory Board.

#### **External validation**

External validation of PSLO are achieved through the following:

- 1) Industry Advisory Board discussions

- 2) Graduate job placement and continuing education rates

- 3) PSLO are aligned and updated to reflect changes to ABET ETAC 2019-2020 Cycle.

# Section 4 – Curriculum Map

|         |       |                                                 |   |   | PSLO |   |   |

|---------|-------|-------------------------------------------------|---|---|------|---|---|

| Course  | Major | Title                                           | 1 | 2 | 3    | 4 | 5 |

| CST 162 |       | Digital Logic I                                 | Х |   |      |   |   |

| CST 130 |       | Computer Organisation                           | Х |   |      |   |   |

| CST 120 |       | Embedded C                                      | Х |   |      |   |   |

| CST 131 |       | Computer Architecture                           | Х |   |      |   |   |

| CST 133 |       | Digital Logic II                                | Х | х |      |   |   |

| CST 134 |       | Instrumentation                                 | Х |   |      | Х |   |

| CST 250 |       | Computer Assembly Language                      | Х | х |      |   |   |

| CST 204 |       | Introduction to Microcontrollers                | Х | х | Х    |   |   |

| CST 231 |       | Digital Systems Design I                        | Х |   | Х    |   |   |

| CST 337 |       | Embedded System Architecture                    | Х | Х | Х    | Х |   |

| CST 315 |       | Embedded Sensor Interfacing & I/O               | Х |   |      | Х |   |

| CST 374 |       | Embedded Project Proposal                       | Х |   | Х    |   |   |

| CST 371 |       | Embedded Systems Development 1 (Junior Project) | Х |   | Х    | Х | Х |

| CST 372 |       | Embedded Systems Development 2 (Junior Project) | Х |   | Х    |   | Х |

| CST 373 |       | Embedded Systems Development 3 (Junior Project) | Х |   | Х    |   | Х |

| CST 471 |       | Embedded Senior Project 1                       | Х |   | Х    |   |   |

| CST 472 |       | Embedded Senior Project 2                       | Х |   | Х    |   |   |

| CST 473 |       | Embedded Senior Project 3                       | Х |   | Х    |   |   |

| CST 331 | СрЕ   | Microprocessor Peripheral Interfacing           | Х | Х | х    | Х |   |

| CST 418 | СрЕ   | Data Comm & Networks                            | Х |   |      |   |   |

| CST 351 | СрЕ   | Digital System Design II                        | Х |   | Х    |   |   |

| CST 344 | CpE   | Intermediate Computer Architecture              | Х |   |      |   |   |

| CST 442 | СрЕ   | Advanced Computer Architecture                  | Х |   |      |   |   |

| CST 455 | ES    | System on a Chip Design                         | Х |   |      |   |   |

| CST 456 | ES    | Embedded System Testing                         | Х |   |      |   |   |

| CST 466 | ES    | Embedded System Security                        | Х |   | Х    | х |   |

| CST 417 | ES    | Embedded Networking                             | Х |   |      |   |   |

| CST 347 | ES    | Real Time Embedded Operating Systems            | Х |   |      |   |   |

Program Student Learning Outcomes

X = Major component, x = minor component

The curriculum map was updated and approved on October 4, 2019.

# Essential Student Learning Outcomes

Essential student learning outcomes are given in the table below at the introduction, practice, and capstone levels.

| ESLO                     | Introduction                    | Practice                          | Capstone                                             |

|--------------------------|---------------------------------|-----------------------------------|------------------------------------------------------|

| Communication            | WRI 121,<br>WRI 122,<br>SPE 111 | WRI 227<br>CST<br>371/372/373/374 | WRI 327 (CET) / WRI<br>350 (ESET)<br>CST 471/472/473 |

| Inquiry and Analysis     | All CST 1xx                     | All CST 2xx                       | All CST 3xx/4xx                                      |

| Ethical Reasoning        | CST 371                         | PHIL 331 - CET<br>CST 372/373     | CST 471/472/473                                      |

| Teamwork                 | SPE 321                         | CST 371,<br>CST 372               | CST 373                                              |

| Quantitative<br>Literacy | MATH 111/112                    | MATH 251/252/253                  | Adv. Math Elective or<br>MATH 465                    |

| Diverse Perspectives     | ANTH 452/ BUS 304               | CST 371/372/373                   | CST 471/472/473                                      |

## Section 5 – Assessment Cycle

The table below is the updated assessment cycle for 2019-2022. The assessment cycle below reflects changes made as a result of the ABET ETAC a-k to 1-5 learning outcomes change. PSLO are assessed in a three year cycle and the ESLO are assessed in a six year cycle. Each PSLO will have two direct measurements (two classes) with one indirect measurement, and each ESLO will have one direct measurement.

| PSLO                                                                                                                                                                                                                                                      | ESLO                     | 2019-2020                                                | 2020-2021                                                | 2021-2022                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------|

| (1) an ability to apply<br>knowledge, techniques, skills<br>and modern tools of<br>mathematics, science,<br>engineering, and technology to<br>solve well-defined engineering<br>problems appropriate to the<br>discipline; (ESLO Inquiry and<br>Analysis) | Inquiry and<br>Analysis  |                                                          |                                                          | CET/ESET: CST 133<br>(Kevin, Pramod)<br>CET: CST 334, 442, 418<br>(Doug)<br>ESET: CST 456 |

| (2) an ability to design solutions<br>for well-defined technical<br>problems and assist with the<br>engineering design of systems,<br>components, or processes<br>appropriate to the discipline;                                                          |                          | CST 315 (Pramod,<br>George)<br>CST 473 (Kevin,<br>Phong) |                                                          | CST 315 (Pramod,<br>George)<br>CST 473 (Kevin, Phong)                                     |

| (3) an ability to apply written,<br>oral, and graphical<br>communication in well-defined<br>technical and non-technical<br>environments; and an ability to<br>identify and use appropriate<br>technical literature; (ESLO<br>Communication)               | Communication            | CST 371 (Mike,<br>Phong)<br>CST 473 (Kevin,<br>Phong)    |                                                          |                                                                                           |

| (4) an ability to conduct<br>standard tests, measurements,<br>and experiments and to<br>analyze and interpret the<br>results; (ESLO Quantitative<br>Literacy)                                                                                             | Quantitative<br>Literacy |                                                          | ESLO<br>CST 337 (Doug)<br>CST 134<br>(George,<br>Pramod) |                                                                                           |

| (5) an ability to function<br>effectively as a member of a<br>technical team. (ESLO<br>Teamwork)                                                                                                                                                          | Teamwork                 | ESLO<br>CST 371 (Mike,<br>Phong)                         | CST 371 (Mike,<br>Phong)<br>CST 231 (Kevin,<br>Pramod)   |                                                                                           |

| N/A                                                                                                                                                                                                                                                       | Diverse<br>Perspectives  |                                                          |                                                          | CST 471 (Kevin, Phong)                                                                    |

| N/A                                                                                                                                                                                                                                                       | Ethical<br>Reasoning     | -                                                        | -                                                        | -                                                                                         |

## Section 6 – Assessment Activity

This year's assessment focused on the learning outcomes below. Note that this follows the a-k ABET from 2018-2019 assessment cycle. We will be assess using the 2019-2020 PSLOs in 2019-2020.

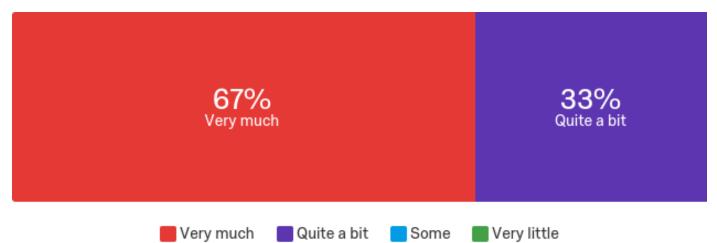

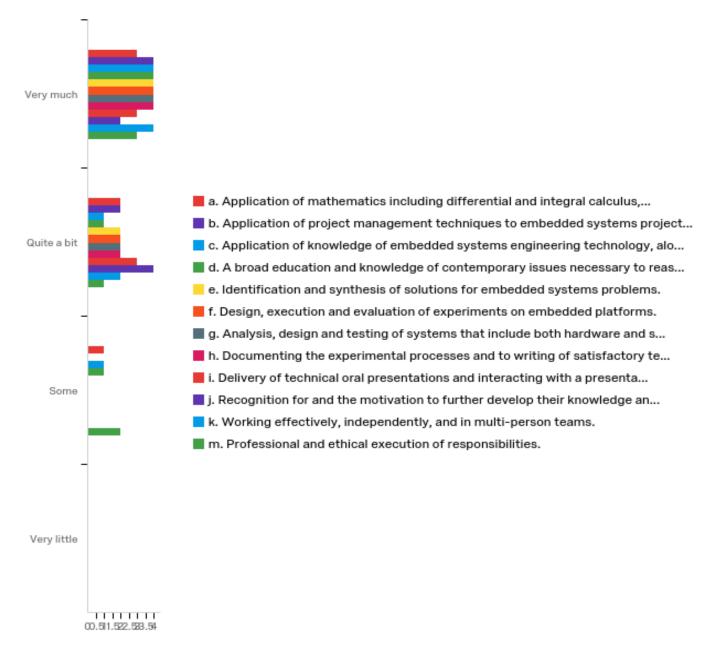

Reference the following table and page numbers. Indirect assessment is provided as Student Exit survey in appendix. The indirect assessment for A,D,E,K indicate that we are meeting the PSLO, although due to small sample size it is not statistically strong.

| Assessment |                                                                                                                          | 2018-19            | Page   | Status         |

|------------|--------------------------------------------------------------------------------------------------------------------------|--------------------|--------|----------------|

|            | 3-year cycle<br>Computer/Embedded Systems<br>Engineering Technology B.S.                                                 |                    |        |                |

| A          | An ability to select and apply the knowledge, techniques, skills, and modern tools of the                                | 471 (Kevin, Phong) | 6, 7   | ок             |

|            | discipline to broadly-defined engineering technology activities;                                                         | 371 (Mike, Phong)  | 8,9    | ОК             |

| D          | An ability to design systems, components,                                                                                | 471 (Kevin, Phong) | 10,11  | ок             |

|            | or processes for broadly-defined<br>engineering technology problems<br>appropriate to program educational<br>objectives; | 371 (Mike, Phong)  | 12,13  | ок             |

| E          | An ability to function effectively as a                                                                                  | 372 (Phong, Mike)  | 14,15  | ОК             |

|            | member or leader on a technical team;                                                                                    | 373 (Phong, Mike)  |        | ок             |

| к          | A commitment to quality, timeliness, and continuous improvement.                                                         | 473 (Kevin, Phong) | 16, 17 | Investigate KF |

|            |                                                                                                                          | 373 (Phong, Mike)  | 18, 19 | ОК             |

#### Assessment A – KF - 471

**Learning Outcome:** An ability to select and apply the knowledge, techniques, skills, and modern tools of the discipline to broadly-defined engineering technology activities

Course/Event: CST 471-473

Level: Capstone

Assessor & Campus: Kevin Pintong at Klamath Falls

<u>Activity</u>: Student submitted final project status memo (requirements) and final project report(Control/innovation) for year-long project.

#### Rubric:

- 1. Project Final Status Memo- Determine how many requirements out of original proposed were met. Score = # requirements met / # requirements not met.

- Timely completion- Did the student successfully complete and demonstrate the project at end of term? Yes = 100% No = 0%

- 3. Final project report grade See Appendix B.

<u>Sample and Reliability</u>: Ten student artifacts assessed. Limited sample size may skew results. Scoring was performed by faculty of record for CST 471.

**Multiple Sites**: Terminology used in assignments are different but same content was covered.

**Performance Target**: Student achieve grade of > 75% according to rubrics for each item.

#### Performance Level:

| ltem |                           | ESET       | CET       |

|------|---------------------------|------------|-----------|

| 1    | Project Final Status Memo | 100% (3/3) | 83% (5/6) |

| 2    | Timely completion         | 100% (3/3) | 83% (5/6) |

| 3    | Final Project Report      | 67% (2/3)  | 67% (4/6) |

|      | Overall                   | 88%        | 77%       |

History of Results: Not Available.

Faculty Discussion: Results are discussed in next cycle.

<u>Interpretation</u>: Data provided in this report indicates that the Program Student Learning Objectives are being met for Klamath Falls. Limited sample size.

#### Assessment A – WL - 471

**Learning Outcome:** An ability to select and apply the knowledge, techniques, skills, and modern tools of the discipline to broadly-defined engineering technology activities

Course/Event: CST 471-473

Level: Capstone

Assessor & Campus: Phong Ngyuen at Wilsonville

<u>Activity</u>: Student submitted Plan, Schedule and Control documents for team-choice, year-long Embedded Project requiring Input, Output, Processor, Control to innovate and/or improve technology.

Rubric: See Appendix A.

**Sample and Reliability**: 4 student artifacts assessed. Limited sample size may skew results. Scoring was performed by faculty of record for CST 471.

Multiple Sites: Terminology used in assignments are different but same content was covered.

Performance Target: Student achieve grade of > 80% according to rubrics

#### Performance Level:

| Item |          | ESET   | CET |

|------|----------|--------|-----|

| 1    | Plan     | 80%    | NA  |

| 2    | Schedule | 80%    | NA  |

| 3    | Control  | 85%    | NA  |

|      | Overall  | 4 of 4 | NA  |

#### History of Results: Not Available.

Faculty Discussion: Results are discussed in next cycle.

<u>Interpretation</u>: Data provided in this report indicates that the Program Student Learning Objectives are being met for Wilsonville. There were time delays in one project. Need to speed up.

#### Assessment A - KF - 371 - Direct

**Learning Outcome:** An ability to select and apply the knowledge, techniques, skills, and modern tools of the discipline to broadly-defined engineering technology activities

Course/Event: CST 371

Level: Capstone

Assessor & Campus: Mike Healy at Klamath Falls

<u>Activity</u>: Student submitted Plan, Schedule and Control documents for team-choice, year-long Embedded Project requiring Input, Output, Processor, Control to innovate and/or improve technology.

Rubric: See Appendix C.

**Sample and Reliability**: Four student artifacts assessed. Limited sample size may skew results. Scoring was performed by faculty of record for CST 371.

Multiple Sites: Terminology used in assignments are different but same content was covered.

Performance Target: Achieve grade of > 80% according to rubrics

#### Performance Level:

#### CST 371

| ltem |          | ESET   | CET  |

|------|----------|--------|------|

| 1    | Plan     | 96%    | 95%  |

| 2    | Schedule | 100%   | 100% |

| 3    | Control  | 95%    | 95%  |

|      |          | 4 of 4 |      |

Successful performance criteria: 85% of teams were able to achieve >80/100 in documents Students were rated on a point scale on rubric for each document

History of Results: Not Available.

Faculty Discussion: Results are discussed in next cycle.

Interpretation: Data provided in this report indicates that the Program Student Learning Objectives are being met for Klamath Falls.

#### Assessment A- WL - 371 - Direct

**Learning Outcome:** An ability to select and apply the knowledge, techniques, skills, and modern tools of the discipline to broadly-defined engineering technology activities

Course/Event: CST 371

Level: Capstone

Assessor & Campus: Phong Ngyuen at Wilsonville

<u>Activity</u>: Student submitted Plan, Schedule and Control documents for team-choice, year-long Embedded Project requiring Input, Output, Processor, Control to innovate and/or improve technology.

Rubric: See Appendix A.

<u>Sample and Reliability</u>: 4 student artifacts assessed. Limited sample size may skew results. Scoring was performed by faculty of record for CST 371.

**Multiple Sites**: Terminology used in assignments are different but same content was covered.

Performance Target: Achieve grade of > 80% according to rubrics

#### Performance Level:

### CST 371

| ltem |          | ESET   | CET |

|------|----------|--------|-----|

| 1    | Plan     | 90%    | NA  |

| 2    | Schedule | 85%    | NA  |

| 3    | Control  | 85%    | 78% |

|      |          | 3 of 3 | NA  |

Successful performance criteria: 85% of teams were able to achieve >80/100 in documents

Students were rated on a point scale on rubric for each document

History of Results: Not Available.

Faculty Discussion: Results are discussed in next cycle.

Interpretation: Data provided in this report indicates that the Program Student Learning Objectives are being met for Wilsonville.

#### Assessment D – KF – 471 - Direct

**Learning Outcome:** An ability to design systems, components, or processes for broadly-defined engineering technology problems appropriate to program educational objectives;

Course/Event: CST 471-473

Level: Capstone

Assessor & Campus: Kevin Pintong at Klamath Falls

Activity: Final Status Project Memo

**<u>Rubric</u>**: Is the project functional? Functionality was determined by calculating percentage of original requirements completed. See Appendix B

**Sample and Reliability**: Nine student artifacts assessed. Limited sample size may skew results. Scoring was performed by faculty of record for CST 471.

Multiple Sites: Terminology used in assignments are different but same content was covered.

**Performance Target**: Achieve grade of > 75% original requirements completed.

#### Performance Level:

| ltem |                                                     | ESET       | CET       |

|------|-----------------------------------------------------|------------|-----------|

| 1    | Project Final Status Memo (% requirements complete) | 100% (3/3) | 67% (4/6) |

#### History of Results: Not Available.

Faculty Discussion: Results are discussed in next cycle.

<u>Interpretation</u>: Data provided in this report indicates that the Program Student Learning Objectives are being met for Klamath Falls. One student was not able to complete the project on time and was given an incomplete. Another student achieved a grade of 65% of original requirements completed, which was the minimum standard set to pass the class.

Given the limited sample size, there is insufficient information to determine whether a change needs to be made to the assessment or the way by which the course is taught.

#### Assessment D - WL - 471

**Learning Outcome:** An ability to design systems, components, or processes for broadly-defined engineering technology problems appropriate to program educational objectives;

Course/Event: CST 471-473

Level: Capstone

Assessor & Campus: Phong Ngyuen at Wilsonville

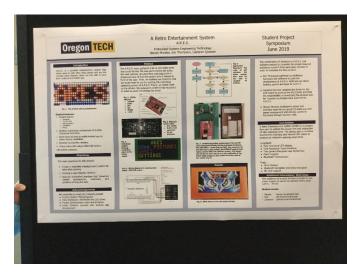

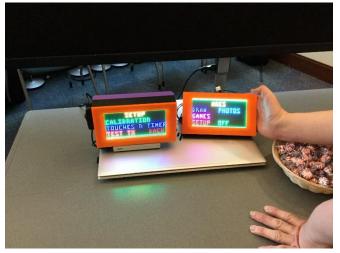

<u>Activity</u>: Senior and Junior projects were required to complete devices built to satisfy all specifications of proposal. Also, projects were completed by using guidelines established by plan, schedule and control documents. All projects are intellectual property of students. If requested, students will demonstrate projects. As an example, below are photos of project, poster and members of one Junior Project team. Project was a Retrograde Game Console.

Rubric: Is the project functional?

<u>Sample and Reliability</u>: Ten student artifacts assessed. Limited sample size may skew results. Scoring was performed by faculty of record for CST 471.

**Multiple Sites**: Terminology used in assignments are different but same content was covered.

**Performance Target**: Achieve grade of > 75% according to rubrics for each item.

#### Performance Level:

| Item |                                             | ESET       | CET |

|------|---------------------------------------------|------------|-----|

| 1    | Project successfully demoed and functional. | 100% (4/4) | N/A |

|      | Overall                                     | 100% (4/4) | N/A |

#### History of Results: Not Available.

Faculty Discussion: Results are discussed in next cycle.

<u>Interpretation</u>: Data provided in this report indicates that the Program Student Learning Objectives are being met for Wilsonville. There were time delays in one project. Need to speed up.

#### Assessment D – KF - 371

**Learning Outcome:** An ability to select and apply the knowledge, techniques, skills, and modern tools of the discipline to broadly-defined engineering technology activities

Course/Event: CST 371-373

Level: Capstone

Assessor & Campus: Mike Healy at Klamath Falls

<u>Activity</u>: Student submitted Plan, Schedule and Control documents for team-choice, year-long Embedded Project requiring Input, Output, Processor, Control to innovate and/or improve technology.

Rubric: See Appendix C

**Sample and Reliability**: Four student artifacts assessed. Limited sample size may skew results. Scoring was performed by faculty of record for CST 371.

Multiple Sites: Terminology used in assignments are different but same content was covered.

Performance Target: Achieve grade of > 80% according to rubrics

#### Performance Level:

| Item |          | ESET   | CET  |

|------|----------|--------|------|

| 1    | Plan     | 96%    | 95%  |

| 2    | Schedule | 100%   | 100% |

| 3    | Control  | 95%    | 95%  |

|      | Overall  | 4 of 4 |      |

#### History of Results: Not Available.

Faculty Discussion: Results are discussed in next cycle.

Interpretation: Data provided in this report indicates that the Program Student Learning Objectives are being met for Klamath Falls.

#### Assessment D – WL - 371

**Learning Outcome:** An ability to select and apply the knowledge, techniques, skills, and modern tools of the discipline to broadly-defined engineering technology activities

Course/Event: CST 471-473

Level: Capstone

Assessor & Campus: Phong Ngyuen at Wilsonville

<u>Activity</u>: Student teams submitted Plan, Schedule and Control documents for team-choice, year-long Embedded Project requiring Input, Output, Processor, Control to innovate and/or improve technology.

Rubric: See Appendix A.

<u>Sample and Reliability</u>: 3 student artifacts assessed. Limited sample size may skew results. Scoring was performed by faculty of record for CST 371.

Multiple Sites: Terminology used in assignments are different but same content was covered.

Performance Target: Achieve grade of > 80% according to rubrics

#### Performance Level:

| Item |          | ESET   | CET |

|------|----------|--------|-----|

| 1    | Plan     | 90%    | NA  |

| 2    | Schedule | 85%    | NA  |

| 3    | Control  | 85%    | NA  |

|      |          | 3 of 3 | NA  |

#### History of Results: Not Available.

Faculty Discussion: Results are discussed in next cycle.

<u>Interpretation</u>: Data provided in this report indicates that the Program Student Learning Objectives are being met for Wilsonville.

#### Assessment E – KF - 372 and 373 – Direct

Learning Outcome: An ability to function effectively as a member or leader on a technical team;

Course/Event: CST 372 and 373

Level: Capstone

Assessor & Campus: Mike Healy at Klamath Falls

Activity: Peer Evaluation.

**<u>Rubric</u>**: Student evaluation surveys were conducted by team members on other team members. Also papers on lessons learned, lay-language project descriptions, and testing were assigned. See appendix for sample submission of a Student Evaluation. Other papers can be provided on request. See Appendix G.

**Sample and Reliability**: Fourteen student artifacts assessed. Limited sample size may skew results. Scoring was performed by faculty of record for CST 372/373.

Multiple Sites: Terminology used in assignments are different but same content was covered.

**Performance Target**: Achieve grade of > 75% original requirements completed.

#### Performance Level:

| ltem |                                            | ESET         | CET         |

|------|--------------------------------------------|--------------|-------------|

| 1    | Peer Evaluations (% requirements complete) | 100% (10/14) | 100% (4/14) |

#### History of Results: Not Available.

**Faculty Discussion:** All team members of all three groups graded all other team members > 75%. Also, papers were overwhelmingly positive.

**Interpretation**: Data provided in this report indicates that the Program Student Learning Objectives are being met for Klamath Falls. Professor evaluations of each team member was also completed.

#### Assessment E - WL - 372 and 373 - Direct

Learning Outcome: An ability to function effectively as a member or leader on a technical team;

Course/Event: CST 372 and 373

Level: Capstone

Assessor & Campus: Phong Ngyuen at Wilsonville

Activity: Peer Evaluation.

**<u>Rubric</u>**: Student evaluation survey were conducted by team members on other team members. Also a paper on leadership and teamwork was assigned. See appendix for sample submission of the Student Evaluation which students used to grade one another. Also, a tally of scores is provided. Papers on leadership/teamwork/lessons learned can be provided upon request. See Appendix E and F.

**Sample and Reliability**: Nine student artifacts assessed. Limited sample size may skew results. Scoring was performed by faculty of record for CST 372/373.

Multiple Sites: Terminology used in assignments are different but same content was covered.

**Performance Target**: Achieve grade of > 75% original requirements completed.

#### Performance Level:

| Item |                                                     | ESET       | CET |

|------|-----------------------------------------------------|------------|-----|

| 1    | Project Final Status Memo (% requirements complete) | 100% (9/9) | N/A |

History of Results: Not Available.

**Faculty Discussion:** All team members of all three groups graded all other team members > 75%. Also, papers were overwhelmingly positive.

**Interpretation**: Data provided in this report indicates that the Program Student Learning Objectives are being met for Wilsonville. Might include professor evaluations of team members next time.

#### Assessment K - KF - 473 - Direct

Learning Outcome: A commitment to quality, timeliness, and continuous improvement.

Course/Event: CST 473

Level: Capstone

Assessor & Campus: Kevin Pintong at Klamath Falls

<u>Activity</u>: Two papers were assigned. One paper was a test plan and the other paper was the final project document submissions.

Rubric: See Appendix B for grading rubric

<u>Sample and Reliability</u>: Ten student artifacts assessed. Limited sample size may skew results. Scoring was performed by faculty of record for CST 471.

Multiple Sites: Terminology used in assignments are different but same content was covered.

**Performance Target**: Achieve grade of > 80% according to rubrics for each item.

#### Performance Level:

| ltem |                                                      | ESET      | CET       |

|------|------------------------------------------------------|-----------|-----------|

| 1    | Score from grading rubric for final report above 80% | 67% (2/3) | 67% (4/6) |

| 2    | Score from grading rubric for test plan above 80%    | 33% (1/3) | 67% (4/6) |

#### History of Results: Not Available.

Faculty Discussion: Results are discussed in next cycle.

**Interpretation**: While the limited sample size is not helpful, there are several reasons to explain the low performance. Some students received job offers which made them decide to do the bare minimum to graduate.

Students also frequently have a difficult time completing the project and test plan in time. For this reason, instructor will consider starting on project in CST 471 sooner. This indicates that an improvement can be made. Improvement and action plan discussed in Section 7.

#### Assessment K - WL - 473 - Direct

Learning Outcome: A commitment to quality, timeliness, and continuous improvement.

Course/Event: CST 473

Level: Capstone

Assessor & Campus: Phong Ngyuen at Wilsonville

Activity: A paper on quality and continuous improvement was assigned and graded to a rubric

Rubric: See Appendix J for grading rubric

**Sample and Reliability**: Four student artifacts assessed. Limited sample size may skew results. Scoring was performed by faculty of record for CST 471.

**Multiple Sites**: Terminology used in assignments are different but same content was covered.

**Performance Target**: Achieve grade of > 80% according to rubrics for each item.

#### Performance Level:

| Item |                                     | ESET       | CET |

|------|-------------------------------------|------------|-----|

| 1    | Score from grading rubric above 80% | 100% (4/4) | N/A |

#### History of Results: Not Available.

Faculty Discussion: Results are discussed in next cycle.

<u>Interpretation</u>: Data provided in this report indicates that the Program Student Learning Objectives are being met for Wilsonville. Limited sample size.

#### Assessment K – KF - 373 – Direct

Learning Outcome: A commitment to quality, timeliness, and continuous improvement.

Course/Event: CST 373

Level: Capstone

Assessor & Campus: Mike Healy at Klamath Falls

Activity: A paper on specific design improvements was assigned and graded to a rubric.

Rubric: See Appendix H for grading rubric

**Sample and Reliability**: Four student artifacts assessed. Limited sample size may skew results. Scoring was performed by faculty of record for CST 373.

**Multiple Sites**: Terminology used in assignments are different but same content was covered.

**Performance Target**: Achieve grade of > 80% according to rubrics for each item.

Performance Level:

| ltem |                                     | ESET       | CET        |

|------|-------------------------------------|------------|------------|

| 1    | Score from grading rubric above 80% | 94% (9/13) | 94% (4/13) |

#### History of Results: Not Available.

**Faculty Discussion:** Specific feedback on content is given prior to submission. Results are kept in file for discussion during final exam week and beyond to next cycle.

<u>Interpretation</u>: Data provided in this report indicates that the Program Student Learning Objectives are being met for Klamath Falls.

#### Assessment K - WL - 372 and 373 - Direct

Learning Outcome: A commitment to quality, timeliness, and continuous improvement.

Course/Event: CST 372/373

Level: Capstone

Assessor & Campus: Phong Ngyuen at Wilsonville

Activity: A paper on quality and continuous improvement was assigned and graded to a rubric

**<u>Rubric</u>**: See Appendix J for grading rubric

<u>Sample and Reliability</u>: Three student artifacts assessed. Limited sample size may skew results. Scoring was performed by faculty of record for CST 372/373.

**Multiple Sites**: Terminology used in assignments are different but same content was covered.

**Performance Target**: Achieve grade of > 80% according to rubrics for each item.

#### Performance Level:

| ltem |                                     | ESET       | CET |

|------|-------------------------------------|------------|-----|

| 1    | Score from grading rubric above 80% | 100% (4/4) | N/A |

#### History of Results: Not Available.

Faculty Discussion: Results are discussed in next cycle.

<u>Interpretation</u>: Data provided in this report indicates that the Program Student Learning Objectives are being met for Wilsonville. Limited sample size.

## Section 7 – Data-driven Action Plans: Changes Resulting from Assessment

### Improvements in Assessment Process:

- <u>Current Cycle (2018-2019)</u>:

- We re-designed three year assessment cycles for PSLOs around new ABET ETAC 1-5 requirements and identified faculty who will collect data.

- We discussed data collected from the previous cycle (2017-2018) in our meeting and determined that we need to collect more detailed data on assignments, and provide better assignment descriptions to show that our students are meeting the PSLO.

- Our dataset for this cycle has been dramatically improved. We have more supporting documentation. Our improvement in coordination between campuses yielded much more standardized and reliable data set between campuses.

- <u>Future (2019-2020):</u>

- We need to make sure that courses between both campuses have alignment in course learning outcomes and PSLOs. Our new curriculum map shows the new PSLOs for this cycle. With George Drouant and Pramod Govindan hired to replace faculty who left or retired, we need to make sure courses are in alignment.

### Action Plan for 2019-2020

Action Driver 1: Assessment data for CST 471/473 – Outcome K.

<u>Action Specifics 1</u>: Kevin Pintong will modify CST 471/472/473 for more development time in CST 471 in the 2019-2020 school year. Many students do not have sufficient time to complete test plans and reports in CST 473 because they are still finishing their project.

**Reassessment:** This outcome will not be reassessed per the ABET ETAC changes for the 2019-2020 cycle.

Action Driver 2 : General assessment activity

Action Specifics 2 : Kevin Pintong will review program courses to make sure courses are well-aligned.

## Section 8 – Closing the Loop: Evidence of Improvement in Student Learning.

No data from previous cycle needed to be re-assessed.

## Section 9 – Contact

## Program Director: Troy Scevers

## Assessment Coordinator: Kevin Pintong

## Data provided by:

Michael Healy Phong Ngyuen Kevin Pintong Office of Academic Excellence

## Assessment A – WL CST 371 and CST 471

## Rubric for project plan

|                                                                                  | Highest level of competence                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timely submission                                                                | 7 pts: final plan submitted by 5:00 pm, Friday of 10th week                                                                                                                                                                                                                              |

| Format/Organization                                                              | 8 pts: inside folder, typed, double space, cover page, table of content, list of figures,<br>list of lables, dividers separating each section                                                                                                                                            |

| Spelling errors                                                                  | 5 pts: each spelling error incurs 1 pt off up to total of 5 pts                                                                                                                                                                                                                          |

| Grammatical errors                                                               | 5 pts: each grammatical error incurs 1 pt up to a total of 5 pts                                                                                                                                                                                                                         |

| Modules                                                                          | 10 pts: break entire design into sensible, smaller modules. Examples of good modules are power supply, transmitting module, receiving module, output module, control module                                                                                                              |

| Hierarchichal design diagrams                                                    | 10 pts: modular block diagrams broken down to top-level diagram which is in turn divided into smaller sub-level diagrams that describe clearly the modules of project. Each block diagram will be backed up by a detailed wiring schematic.                                              |

| Diagram explanation                                                              | 20 pts: provide precise write-up/explanation of each diagram. Any assembler without deisgn knowledge should be able to read the diagrams and explanation and be able to assemble the device.                                                                                             |

|                                                                                  |                                                                                                                                                                                                                                                                                          |

| Test Plan                                                                        | 15 Pts:Provide a step by step test plan broken down to plan for each sub-modules, modules, module integration and final product test.                                                                                                                                                    |

|                                                                                  |                                                                                                                                                                                                                                                                                          |

| Update parts list/commitment to certain percentage of variation preliminary list | 5 pts: provide updated parts list (wish list). Annotate parts that the team has in hand.<br>Prof. N will insist on seeing and touching ALL parts of parts list to compare with parts<br>list. 20% off for each missing major part (microcontroller, PLD, input, output, power<br>supply) |

| Software requirements                                                            | 10 pts: provide UML or flow charts of ALL software to be used. Must have written at least 20% of actual source code. Any hardware sophomores should be able to read your software requirements and proceed with ease to complete all source code of the project.                         |

| Preliminary cost                                                                 | 5 pts: estimated total cost. Estimated parts/packaging cost, engineering cost, labor cost, outsourced contract cost Tabular format. Clear explanation of basis for estimation. Provide and explain estimated errors of estimated cost.                                                   |

| Team assignment                                                                  | 5 pts: Identify assigments/responsibilities of each                                                                                                                                                                                                                                      |

| Rubric for project schedule                                                      |                                                                                                                                                                                                                                                                                          |

|                                                                                  | Highest level of competence                                                                                                                                                                                                                                                              |

| Timely submission                                                                | 5 pts: final schedule submitted by 5:00 pm, Friday of 10th week                                                                                                                                                                                                                          |

| Format/Organization                                                              | 10 pts: inside folder, typed, double space, formatted in some timeline fashion                                                                                                                                                                                                           |

| Spelling errors                                                                  | 5 pts: each spelling error incurs 1 pt off up to total of 5 pts                                                                                                                                                                                                                          |

| Scheduled dates for start and receipt of major parts purchased                   | 10 Pts: major parts examples are microcontroller, wireless, power supply Do not worry minor parts like wires, headers                                                                                                                                                                    |

| Actual dates for start and receipt of major parts purchased                                                         | 10 Pts: annotate when parts were actually purchased and received in order to compare                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Schechuled dates for start and completion of each schematic in plan                                                 | 10 pts: shedule for work on schematic of each module. Apart from minor testing, try not hook up hardware until schematic is done.                                                                                                                                                                     |

| Scheduled dates for hardware<br>and software start and<br>completion of each module as<br>specified in plan         | 10 Pts: once schematic and flow chart/UML are completed, wiring and coding must be scheduled                                                                                                                                                                                                          |

| Scheduled dates for integration<br>of modules. Be as detailed as<br>possible on this part                           | 10 Pts: schedule this keeping in mind the requirement that modules must be finished and tested indivually before integration                                                                                                                                                                          |

| Scheduled dates for individual testing of major parts                                                               | 10 Pts: make sure these dates are coordinated with testing of modules                                                                                                                                                                                                                                 |

| Scheduled dates for testing of each module and integration of all modules                                           | 10 Pts: coordinate this with arrival of parts and testing of integration and final testing                                                                                                                                                                                                            |

| Annotate who are the primary<br>and secondary parties<br>responsible for which part,<br>which module, which testing | 10 Pts: self explanatory                                                                                                                                                                                                                                                                              |

| Rubric for control                                                                                                  |                                                                                                                                                                                                                                                                                                       |

|                                                                                                                     | Highest level of competence                                                                                                                                                                                                                                                                           |

| Timely submission                                                                                                   | 5 pts: by 5:00 pm of Friday, 10th week                                                                                                                                                                                                                                                                |

| Format/Organization                                                                                                 | 5 pts: typed, double space in some formatted fashion                                                                                                                                                                                                                                                  |

| Spelling errors                                                                                                     | 5 pts: each spelling error incurs 1 pt off up to total of 5 pts                                                                                                                                                                                                                                       |

| Grammatical errors                                                                                                  | 5 pts: each grammatical error incurs 1 pt up to a total of 5 pts                                                                                                                                                                                                                                      |

| Firing of a group member                                                                                            | 10 pts: Prof. N has a control measure for firing of a group member. What is the group's control measure before taking it up with the big N?                                                                                                                                                           |

| Habitual absence in meeting                                                                                         | 10 pts: how many meetings can a member miss? What if someone misses too many meeting?                                                                                                                                                                                                                 |

| Missing deadline in ordering parts                                                                                  | 10 pts: how does one track if someone has ordered parts or not? Having a schedule does not allow one to assume that responsible parties will follow schedules. If an ordering deadline is found to be missed what will be done to get the parts on time? What will become of the responsible parties? |

| Parts not arriving by scheduled arrival date                                                                        | 5 pts: whether parts are late due to late ordering or irresponsible vendors or long delivery time, one still must have parts by scheduled receipt date. What happens if parts does not arrive on time? What can be done, who will do it?                                                              |

| Module schematic delay                                                                                              | 10 pts: what happens if schematic of each module is delayed? How much time can it be delayed? What happens if someone has to take over? Who will take over if it comes to that?                                                                                                                       |

| Module hardware and software delay                                                                                  | 10 pts: What happens if the hardware and software are not completed for a module for whatever reasons? What possible reasons could cause delays: bad schematic, parts, interface? Account for all possible delays!                                                                                    |

| Module integration delay                                                                                            | 10 pts: What if all modules cannot be integrated by scheduled date? Identify all possible reasons for delays and actions that must be taken to alleviate the situations!                                                                                                                              |

| Annotation on schedule of ALL delays/problems | 10 pts: how will you update the initial schedule if there are delays? DO NOT simply word process the schedule so that years from now it looks like no delays/problems took place. Find a way to annotate the schedule to show in details all problems and actions taken. |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Firing of Prof N                              | 5 pts: what if the person responsible for failure of project is big N. Be serious about this! If it is, what measures will you take!                                                                                                                                     |

# Appendix B

## Assessment A – KF CST 473

|            | Project Final Status | Timely     | Project Final | Test |

|------------|----------------------|------------|---------------|------|

|            | Memo                 | Completion | Report        | Plan |

| Сре        |                      |            |               |      |

| Student 1  | 92.65                | 100        | 100           | 100  |

| СрЕ        |                      |            |               |      |

| Student 2  | 95                   | 100        | 100           | 95   |

| СрЕ        |                      |            |               |      |

| Student 3  | 100                  | 100        | 95            | 100  |

| СрЕ        |                      |            |               |      |

| Student 4  | 92                   | 100        | 90            | 73   |

| СрЕ        |                      |            |               |      |

| Student 5  | 0                    | 0          | 0             | 0    |

| Сре        |                      |            |               |      |

| Student 6  | 63                   | 100        | 72.5          | 67   |

|            |                      |            |               |      |

| ES Student |                      |            |               |      |

| 1          | 83.75                | 100        | 64.5          | 64.5 |

| ES Student |                      |            |               |      |

| 2          | 97                   | 100        | 90            | 90   |

| ES Student |                      |            |               |      |

| 3          | 79                   | 100        | 92.5          | 85   |

# Test Plan Grading Rubric (Appendix B)

| Test plan grading rubric |   | Include?                                                                                                                                                                                                                          | Possible |    |

|--------------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----|

| Introduction             |   | 1                                                                                                                                                                                                                                 | 10       |    |

|                          |   | System Block diagram                                                                                                                                                                                                              | 1        | 10 |

| 3.1                      | b | Software Requirements                                                                                                                                                                                                             | 1        | 10 |

|                          | с | Explanation on how each requirement and corresponding subrequirement has been met through a specific test you developed. Data is shown and included in plan                                                                       | 1        | 20 |

|                          | d | Provide a chart of how code is structured/organized. Your choice<br>on diagram (Block diagram, flow chart, ASM, UML, State<br>machine, etc.)                                                                                      | 1        | 10 |

|                          | е | List all tools used to generate the code. Compliers, synthesizers, IDEs, etc. It is important to indicate the exact version of each piece of software. Also list all external code you may have used such as libraries, API, etc. | 1        | 10 |

|                          | f | Notate any external code that you have used on this project.                                                                                                                                                                      | 1        | 5  |

|                          | g | Provide a listing of all functions with declaration, input, return types, and possible failure conditions, and how the function was/will be tested.                                                                               | 1        | 10 |

|                          | h | Timing if applicable                                                                                                                                                                                                              | 0        | 10 |